Jinhang Choi

I am working in Deep Neural Network (DNN) HW/SW Co-design & Optimization.

I am working in Deep Neural Network (DNN) HW/SW Co-design & Optimization.

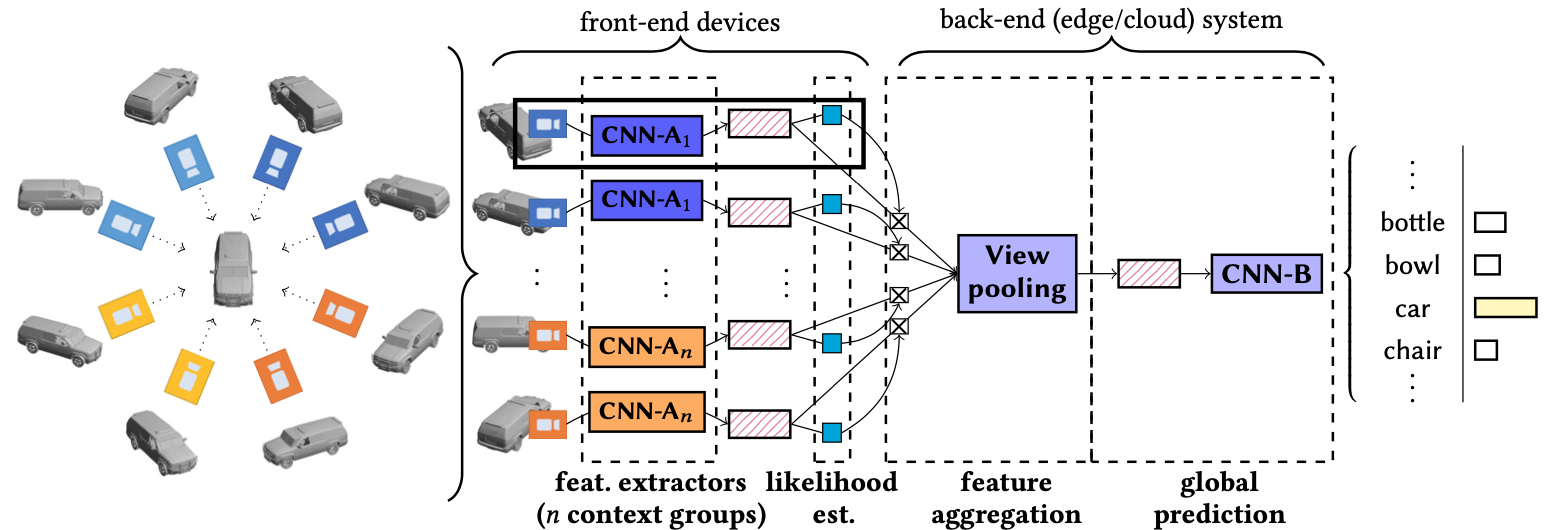

Dissertation: Context-Aware Design and Optimization of Embedded DNN Architectures, co-advised by Prof. Vijaykrishnan Narayanan and Prof. John (Jack) Sampson

Presented a) hardware/software co-design to mitigate excessive off-chip memory access caused by Deep Neural Networks (DNN), b) DNN memory footprint reduction scheme to expedite training speed in approximate computing, and c) iterative functional verification methodology to validate DNN design in machine learning.

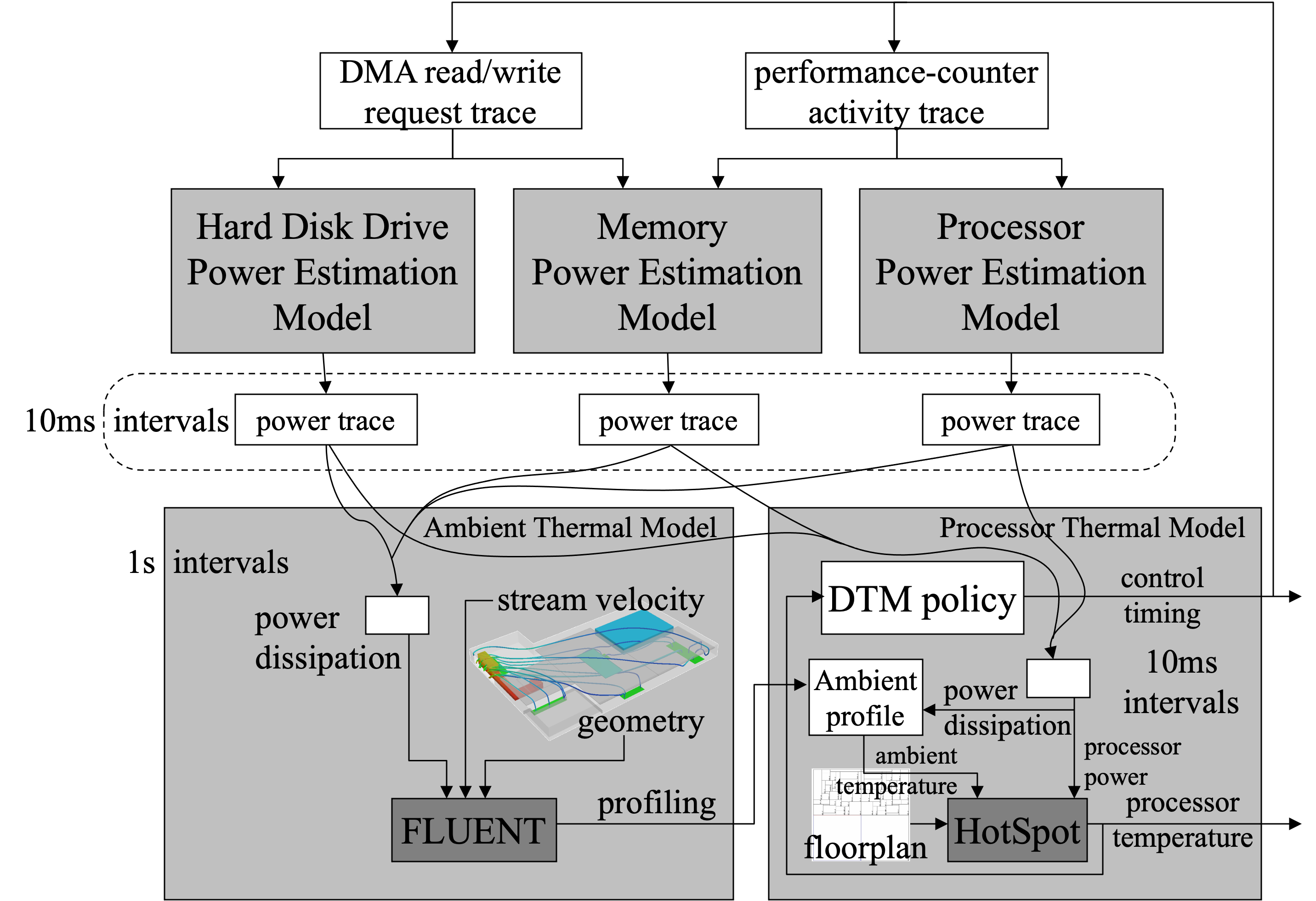

Thesis: A Novel Thermal Simulation Framework to Reflect Ambient Changes, advised by Prof. Sung Woo Chung

Proposed a system-wide thermal simulation framework for computer architecture design that reflects ambient temperature changes, by using the mechanical heat flow model as well as microarchitectural performance event-based thermal model.

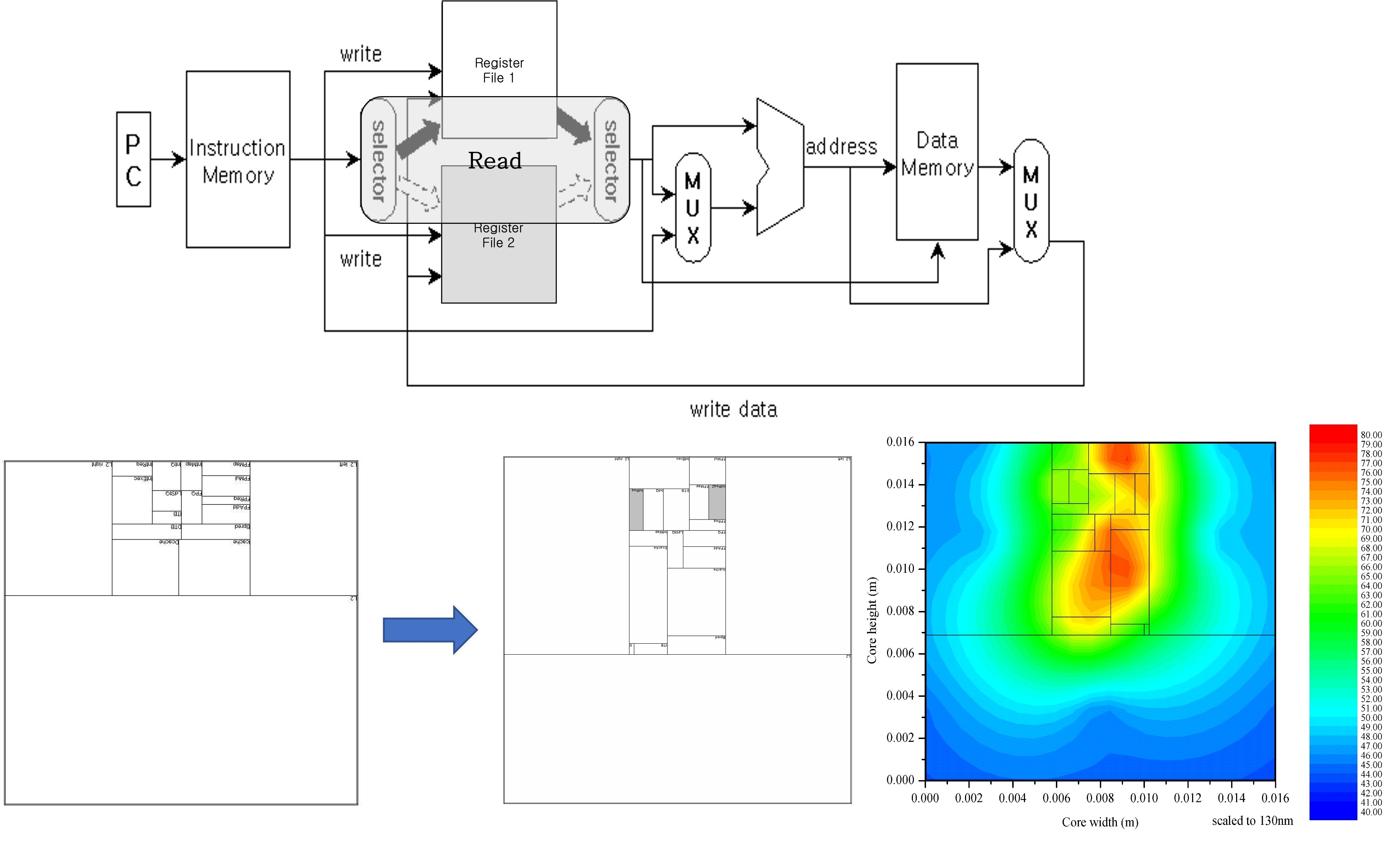

Undergraduate Research Project: A Dual Integer Register File Structure for Temperature-Aware Microprocessors

Member of Convergence for High-Efficiency Formulations (CHEF).

Member of AI Frameworks (AIFX). Profiled & optimized Large Language Models (LLMs) for Maia Software Development Kit (Maia SDK), where I designed Standard Kernel Library (SKL) integrated with PyTorch ATen interface. It supported the end-to-end inference of LLMs, including GPT-3.5-Turbo, Mistral, Llama-2 and 3.

Member of Cloud AI Systems & Technologies (CAST). Designed Neural Processing Unit (NPU) microarchitecture for Microsoft Floating Point (MSFP) transform/quantization, and its memory layout [bib]. The RTL/IP prototype demonstrated ONNX Runtime in Intel Stratix10 NX FPGAs with Azure build pipeline automation.

Member of MDL. Conducted research to realize distributed intelligence for embedded visual recognition system. Experimented with the impact of near-data processing on Deep Neural Network (DNN) training & inferencing from the perspective of performance, energy, and accuracy. The studies led to designing DNN-based hardware systems in FPGA platform and Andriod/Linux mobile platforms. Consequently, in the course of this role, published 6 conference papers and 1 journal paper.

Intern at AI and Advanced Architectures (AIArch) of Azure Hardware Systems Group. Deployed Microsoft deep learning inference platform, BrainWave, on Intel Stratix10 GX FPGAs. To enable this transition, upgraded Intel FPGA IP generation, ported the latest FPGA synthesis compiler (a.k.a. Intel QuartusPro 19) on Azure cloudbuild service, verified and corrected the existing BrainWave Neural Processing Unit hardware system designs from automated test suite (pytests). This design exploration also projected FPGA resource estimation and its corresponding restriction to support additional functionalities required in AI inference service, which offered new challenges & opportunities with Microsoft hardware designers.

Intern at AI and Research (AI+R) Group. Deployed a Machine Reading Comprehension (MRC) model on BrainWave platform. To port the MRC TensorFlow model, modified a graph compiler to offload TensorFlow subgraph, wrote a subgraph firmware for FPGA acceleration based on Instruction Set Architecture (ISA) of BrainWave Neural Processing Unit, then verified its execution on Intel Arria10 FPGAs. It was a working example that firmware developers could leverage to accelerate AI inferencing service in BrainWave plaform.

Proposed and graded homeworks of undergraduate class, data structures and algorithms, in Fall 2015/Spring 2016.

Member of start-up company, LineWalks. Led Online Analysis Processing (OLAP) system design. Deployed Apache Tajo SQL-on-Hadoop engine on clusters of commodity computer systems, thereafter I developed extract/transform/load (ETL)-OLAP interface for geolocation-based medical infographic project.

Member of SMRL. Conducted study & research to design temperature-aware computer system. To alleviate performance degradation caused by on-chip thermal hotspot problem, developed a computer system-wide CPU/DRAM/HDD activity tracer based on hardware performance event counter monitoring interface. Then, simulated power consumption and correponding on-chip temperature behaviors in the level of Linux operating systems. In the course of this role, presented 1 poster, and published 3 conference papers and 4 journal papers (1 IEEE journal / 3 Korea domestic journals).

Proposed and graded the projects of undergraduate class, Computer Architecture: 1) Implementation of single-cycle Instruction Set Architecture (Simple MIPS) on verilog, and 2) performance modeling & analysis based on microarchitectural simulatior, SimpleScalar.

Intern at SMRL. Conducted study & research to design temperature-aware microarchitecture. To mitigate on-chip thermal hotspot problem, developed a microarchitectural simulator that incorporates microarchitectural modeling (SimpleScalar), architectural power estimation (Wattch), and thermal behavior analysis (HotSpot), then experimented with architectural changes from the perspective of performance, power, and temperature. In the course of this role, published 1 Korea domestic journal paper.